(中国电子科技集团公司第三十四研究所,广西 桂林 541004)

摘要:本文先是简要的介绍了目前环境下的国产化需求,引出目前E1接口电路主要使用进口专用芯片的背景,接着详细说明了使用国产FPGA和国产硬件电路实现E1接口电路的设计思路和方案。

关键词:国产化,E1接口电路,FPGA

Abstract: This paper first briefly introduces the localization demand in the current background,then introduce the backdrop that the current E1 interface circuit mainly uses imported special chips,and then describes in detail the design idea and scheme of using domestic FPGA and domestic hardware to realize E1 interface circuit.

Key words: localization, E1 interface circuit, FPGA。

在贸易摩擦的大背景下,相互之前的竞争开始触及到更深更多的层面。在面临随时会被进口芯片卡脖子的情况下,国产化替代已经成为当前国家和产业发展最紧要的事情。在以往时候,系统设备的电路方案主要使用进口芯片这样成熟的应用方案,目前,随着国家对国产化替代越来越重视,许多设备开始研究国产化方案,研制国产化产品。

E1接口作为PCM设备、SDH设备的必备接口,应用十分广泛。目前主要使用进口的或者外资控股厂家的专用接口芯片来实现E1信号的发送接收,HDB3编解码的功能,目前国内没有替代进口E1接口芯片的专用自主可控国产芯片。本文尝试使用其他功能芯片搭建E1接口电路,实现进口E1接口芯片的功能,试验结果满足标准要求。

E1是ITU-T制定并有欧洲邮政与电信协会(CEPT)命名的数字传输系统一次群(即PCM30)标准,由32个64kps的PCM话音经过分时复用形成,其传输速率为2.048Mbps,其中30个时隙传输语音等用户信息,另外两个时隙作为系统开销,传输同步码、信令及其他辅助信号。E1接口的物理及电特性符合CCITT的G.703标准。我国也采用E1标准作为PCM系统和N-ISDN的基群。目前,建立在G.703基础上的E1接口在分组网、帧中继网、GSM移动基站及军事通信中得到广泛应用,传输话音、数据、图像等业务。

HDB3(HighDensity Bipolarof order 3code三阶高密度双极性码是在AMI码的基础上改进的一种双极性归零码.它除具有AMI码功率谱中无直流分量.可进行差错自检等优点外.还克服了AMI码的长连0串现象,有利于信息在信道中传输.以及在接收端对定时信号进行提取。而且HDB3码频谱能量主要集中在基波频率以下,占用频带较窄.适用于SDH中2Mb/s线路(即E1信号)。

目前E1接口电路的设计大多是通过专用的进口E1芯片搭配变压器的方案如图1所示。通过阅读进口芯片资料可以得知接口芯片主要提供HDB3极性变换、HDB3编解码、信号整形、LOS告警等功能,结合进口芯片功能和E1接口相关标准采用国微电子FPGA(SMQ7K325TFFG900IP)+国微电子差分接收芯片SM34LV86+国微电子驱动器芯片SM164245PA+赛狐电子变压器SH1065的全国产化方案实现E1信号的收发以及码型转换如图2所示。

图1进口专用E1芯片电路框图

图2国产E1接口电路框图

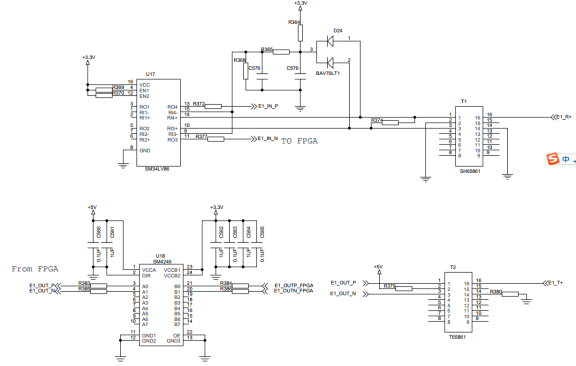

E1接口硬件电路有接收电路和发送电路组成如图3所示,

接收电路由变压器、差分接收芯片、FPGA组成。变压器作用是极性变换,接收方向将双极性的HDB3信号转为两路单极性的HDB3信号,需要带抽头变压器,且匝比为1CT:2CT;差分芯片的作用是通过比较接收电平阈值电路预设的电平和两路单极性的HDB3信号的电平,当单极性的HDB3信号的电平高于预设的电平时输出1,反之输出0;FPGA负责HDB3的解码、信号监测输出告警、提供环回等功能。经测试可正常接收E1测试仪的数据,误码率为0,且允许衰减为6db,满足CCITT的G.703的要求。

发送电路由FPGA、驱动器、变压器组成。FPGA负责HDB3的编码工作;驱动器的作用是完成3.3V到5V的电平转换;变压器将驱动器输出的两路单极性的HDB3信号转为双极性的HDB3信号发送,通过调整抽头上拉电阻可使E1发送信号满足CCITT的G.703要求的接口物理特性。经过测试,发送眼图符合要求。

图3E1接口硬件电路图

1、将消息代码变成AMI码;

2、检查AMI码中是否有四个或者四个以上的0。如果有,将第四个0,设置成V极性和它前面的第一个l极性相同;

3、检查加v后的AMI码,如果两个V之间有偶数个l。就将最后一个l后面的0设置成B极性和它前面的l的极性相反;使后面的非0符号从V开始继续变化,即V的符号和B的符号一致,并再交错变化。

5.1.2.HDB3编码的电路设计

在实际信号处理的过程中,不能像编码规则那样:首先把代码串变换成AMI码,完成插“v”插“B”工作之后,再依据编码规则变换“+l”和“一l”的极性。这样做需要大量的寄存器,同时电路结构也变得复杂。在这里,首先完成插“V”工作,接着执行插“B”工作,最后实现单极性变双极性的信号传输。这样一来输入进来的信号和插“v”插“b”功能电路中处理的信号都是单极性信号,需要的寄存器的数目大大减少。

插“V”模块的功能实际上就是对信息代码里的四连O串的检测。即当出现四个连0串的时候,把第四个“O”变换成符号“V”(“V”可以是高电平一1),而在其他情况下则保持信息代码的原样输出。“V”用“ll”表示、“l”用“0l”表示、“0”用“00”表示,插“B”模块的功能是保证附加“V”符号后的序列不破坏“极性交替反转”造成的无直流特性。即当相邻“V”符号之间有偶数个非0符号的时候,把后一段的第一个“0”变为一个非破坏符号“B”符号。由于涉及到一个由现在事件的状态决定过去事件状态的问题,采用一个四位移位寄存器来解决。

根据HDB3的编码规则,“V”的极性是正负交替的,余下的“l”和“B”看成一体且是正负交替的,同时满足“V”的极性与前面的非0码极性一致。由此我们可以将其分别进行极性变换来实现。

5.2.HDB3码解码原理和电路设计

5.2.1.HDB3码的解码原理

根据编码规则,破坏点“V”脉冲与前一个脉冲同极性。因而可从所接收的信码中找到“V”码,然后根据加取代节的原则,“V”码与前面的三位代码必然是取代码。在解码时,需要全部复原为四连O,主要找到“V”码,不管“V”码前是两个“0”码还是3个“0”码,一律把取代节清零,完成扣“V”和扣“B”功能,进而得到原来的信码。根据以上解码原理,HDB3的解码步骤可分为三步:

1、扣“V”:即检测信号中的1001或_100_l串,若检测到,则把100l或_100_l变为0000;

2、扣“B”:即检测信号中的10001或_1000_1串。如果检测到,则把10001或_1000_1变为10000或_10000;

3、极性转换:由于前面来的信号中有“Ol”和“10”,即“+l”和“一1”。而实际情况是:数字电路中只有0和1,所以要进行极性转换,把双极性信号变为单极

性信号,使信号中只含有0和l。

5.2.2.HDB3码的解码电路实现

1、扣“VOOOV”:当收到两相邻的脉冲极性相同时,其中后一个必定是“V”码,将其恢复为0。具体操作时,我们定义一个五位寄存器data buff[4:0],用它来检测信号中的10001或_1000_1,一旦检测到,将他们的值分别变为10000或_10000;

2、扣“B’:检测到的“V”码向前数第三个码,如果它不为0,则表明是补码“B”,将其恢复为0。具体操作时,我们定义一个四位寄存器data_buftf[3:0],用这个寄存器来检测100l或_100_1,一旦检测到,将他们的值都变为0000;

3、极性转换:极性转换主要是将双极性信号转换为单极性信号,将双极性的“lO”码和“Ol”码都转变成单极性“l”码,双极性的“00”码转变成单极性“O”码。

文中主要讨论了使用国微电子FPGA(SMQ7K325TFFG900IP)+国微电子差分接收芯片SM34LV86+国微电子驱动器芯片SM164245PA+赛狐电子变压器SH1065搭建E1接口电路的软硬件设计思路和设计方案。本设计采用全国产的器件,技术方案完全是可行的。测试结果表明,该设计的技术指标达到了设计要求,具有非常广阔的应用前景。

参考文献:

[1] 崔洲涓,胡辽林. SDH中HDB3编解码电路的FPGA实现[J].光通信技术,2011 (3).